Test Solution for CPO Co-packaged Optics

What is CPO? Why is the co-packaged optics technology the key to AI chip performance?

With the widespread application of generative AI, the requirements for chip transmission rates have been rising at an unprecedented pace. Traditional optical modules are thus evolving into more powerful CPO modules in subsequent product iterations.

CPO, or Co-packaged Optics as the name suggests, has become the primary adoption mode for leading AI chip manufacturers.

CPO is replacing traditional optical modules due to its technical features that reduce transmission loss and cut power consumption. Given the enormous demand for AI applications, which entails massive power requirements, components with lower power consumption and higher transmission speeds are more favored by major manufacturers in the entire system.

For manufacturers engaged in CPO testing, the optimization of CPO test solutions is our core focus.

We start with an analysis of the CPO structure.

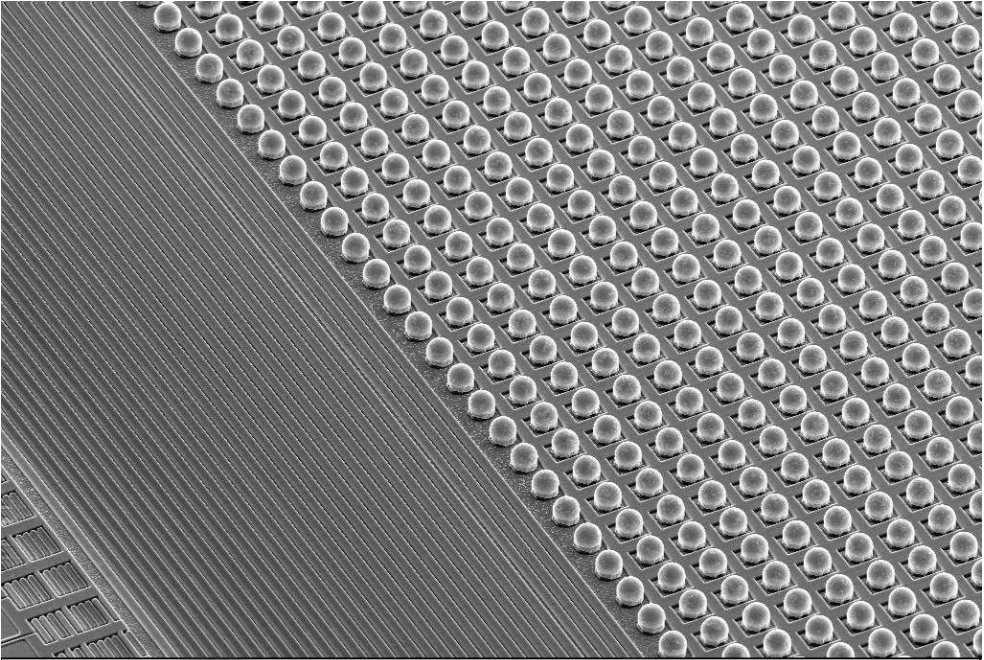

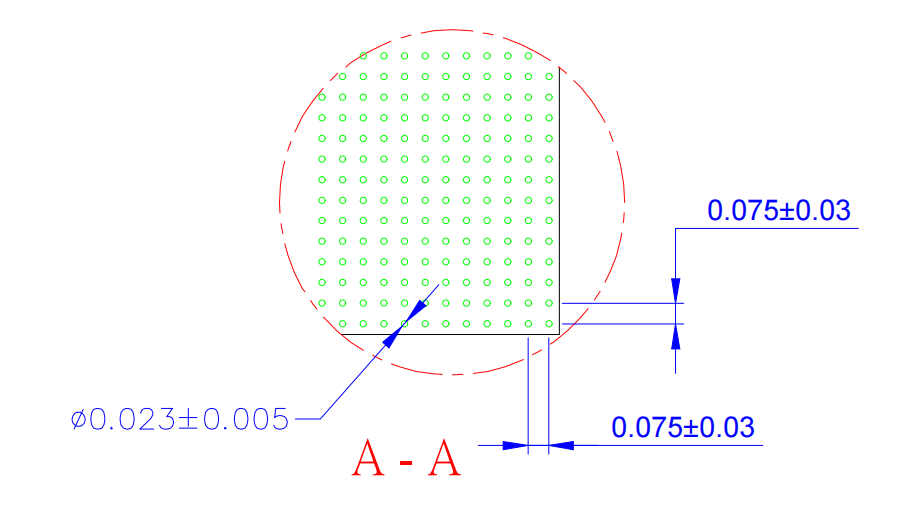

(As shown in the diagram) BGA packaging is adopted for CPO, featuring a ball grid array structure. Micro bumps are also integrated into the internal co-packaged substrate.

CPO Testing Processes

The testing processes of CPO include burn-in, temperature cycling, humidity and heat stress testing, and long-term stability verification.

Wafer-level test.

This test primarily conducts electro-optical performance testing on silicon photonic chips, lasers, modulators and photodetectors at the wafer level to ensure product yield. The core objective is to screen out defective dies and prevent them from entering the subsequent packaging process.

Die/Chip-level Test.

This test is focused on performance verification of single bare chips (including lasers, modulators and photodetectors).

Optical engine/sub-module test.

This process involves the alignment and coupling of photonic chips and electronic chips on a silicon photonics platform to form optical engines or sub-modules, all completed at packaging facilities.

Module-level test.

It refers to the functional verification of fully packaged CPO modules, covering optical ports, signal integrity and electro-optical interfaces.

Final test.

This stage incorporates burn-in testing, temperature shock testing, humidity and heat stress testing, and long-term stability testing.

Every testing process is critical to the delivery of CPO products.

Typical CPO Test Pitch Specifications

| Level | Typical Pitch | Typical Ball Diameter | Function |

|---|

| System Level | 1.0mm / 0.8mm | 0.6mm / 0.5mm | Communication between module and PCB |

| Module Level | 0.4mm / 0.3mm | 0.25mm / 0.2mm | Interconnection of internal components |

| Chiplet Level | < 150μm | < 50μm | High-bandwidth 2.5D/3D packaging |

Pre-packaging Testing

For the pre-packaging stage, our rubber socket can be used to test micro bumps. The gold wires of the rubber socket feature a pitch of 75μm, which can capture electrical signals from micro bumps to achieve electrical conduction.

Advanced global manufacturing processes are advancing toward the 10μm node, yet mainstream micro bump packaging structures remain in the 50-100μm range—our test products fully cover this specification range.

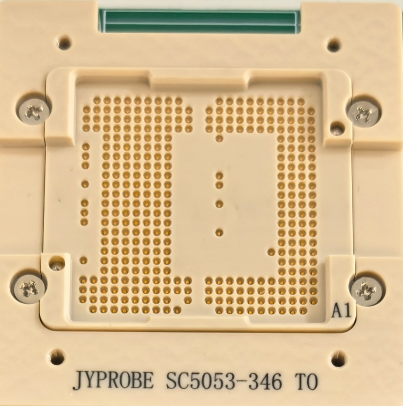

The diagram displays our manual test socket; for automated testing, an open-type socket can be selected to improve efficiency. In addition, we have developed an optimized thermal design and adopted our patented graphene heat dissipation technology, which transfers heat from the chip to graphene, then to metal heat sinks, and finally dissipates it via fans.

The gold wire density of our products can reach 50μm, and we are currently developing solutions to achieve an even smaller and denser pitch of 30μm.

Leveraging high gold wire density for testing smaller micro bumps enables efficient detection of bump status without causing any damage to the bumps.

Post-packaging Testing

For chip testing of products after package assembly, test sockets with a pitch of 0.4mm-1.0mm are available for optical modules, matching the 0.4mm-1.0mm test solution.

Mechanical Structure & Thermal Management

CPO or high-performance ASIC chips typically have a power consumption exceeding 500W-800W during testing.

Active Cooling

The socket lid must integrate liquid cooling or high-power heat sinks to ensure stable junction temperature (Tj) during testing and prevent pin misalignment caused by thermal expansion.

Force Management

An 800G chip may have thousands of BGA pins. With a single pin contact force of 30g, the total applied force can reach several hundred kilograms.

When selecting test sockets, the rigidity of the socket substrate must be verified to prevent contact failure caused by substrate bending under high pressure.